**Original Article**

# Design and Investigation of Hetero Vertical TFET with Source Pocket for Work Function Engineering and Analog Performance Enhancement

Kavindra Kumar Kavi<sup>1</sup>, Ravi Kumar<sup>2</sup>, Suman Dass<sup>2</sup>, Chetna Sinha<sup>2</sup>, Manjeet Singh Sonwani<sup>2</sup>, Lavi Tyagi<sup>3</sup>

<sup>1</sup>Department of ECE, Motilal Nehru National Institute of Technology Allahabad, Utter Pradesh, India.

<sup>2</sup>Department of Electronics and Telecommunication Engineering, Government Engineering College Raipur,

Chhattisgarh, India.

<sup>3</sup>G.B. Pant University of Agriculture and Technology, Uttarakhand, India.

<sup>1</sup>Corresponding Author : kkavi@mnnit.ac.in

Received: 17 March 2024Revised: 17 April 2024Accepted: 14 May 2024Published: 29 May 2024

**Abstract** - To provide a high-efficiency device, this article presents a Vertical SiGe Tunnel Field Effect Transistor (Hetero-VTFET), including and not including a source pocket. For perhaps the first time, a group IV miscible alloy SiGe is exploited in the source to improve carrier tunnelling through a source (SiGe)-channel (Si) Hetero-junction. To establish an optimal Hetero-VTFET design, work function engineering and hetero-junction structure tuning are used. The simulation results carried out using the TCAD Silvaco tool are used to analyze the behaviour of developed Hetero-VTFETs. The proposed optimal structure has a higher  $I_{ON}/I_{OFF}$  ratio (>10<sup>14</sup>), a lesser subthreshold swing (<25 mV/Dec), and a high  $I_{ON}$  current in the 10<sup>-5</sup>A/µm range.

Keywords - Vertical Tunnel Field Effect Transistor, Source pocket, Low supply voltage, Ambipolarity, Subthreshold slope.

## **1. Introduction**

Holistic scaling, which requires both device size and voltage to be reduced, has been proven to be a successful means of lowering power dissipation. However, this aggressive scaling of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) with time leads to physical limits owing to various short channel effects. Scaling both size and voltages at the same time results in a scaled on-state current and a higher leakage current, which is unfavourable. As a result, decreasing both power dissipation and leakage current at the same time remains a complex problem [1]. In order to get a low off-state current, one of the most critical criteria is to reduce the device's Sub-threshold Swing (SS) at room temperature. A normal Field-Effect Transistor's (FET) SS, on the other hand, is restricted to 60mV/decade. The SS is a temperature-dependent variable because the current generation mechanism in a typical FET is dependent on thermionic emission.

To overcome these issues, researchers are looking for alternatives to MOSFETs that could be used in the near future. Because of their unique features, Tunnel Field-Effect Transistors (TFETs) are being viewed as a potential alternative for MOSFETs. TFETs look promising as they can operate at ultra-low supply voltages, while on the other, instead of thermionic emission, TFETs use Band-ToBand Tunnelling (BTBT) method to generate current [2-6]. The gate modulates the channel surface potential in TFETs to govern its control over BTBT tunnelling. BTBT reduces the temperature sensitivity of the SS, allowing the SS to be below 60 mV/decade in TFETs, and therefore, the leakage current in TFETs is lower than that in FETs.

Although TFETs have a low off-state current, they have a lower on-state driving current ( $I_{ON}$ ) than FETs due to their poor BTBT efficiency [7, 8]. On the source side, using heterostructure materials with a short bandgap is amongst the most often utilised strategies for  $I_{ON}$  enhancement. Using a lower bandgap material at the source side tunnelling junction lowers the tunnelling barrier, resulting in a lower threshold voltage ( $V_T$ ) and better  $I_{ON}$  [9-13].

It is observed that source pocket-designed TFETs have improved subthreshold properties than regular TFETs [14, 15]. Materials having lower bandgaps like germanium and InAs are predominantly employed in the source region of a Si-TFET to form a hetero-junction, reducing the tunnelling width and increasing the drain current at the cost of a substantial increase in Ioff  $(10^{-12}A)$  significantly more than the maximum value attained in traditional Silicon based TFETs [16]. However, it has been demonstrated that staggered heterojunctions at the source-channel interface based on III–V materials are ideal for low-voltage operation while balancing power consumption and performance [17]. In light of the preceding, this study presents a V-TFET based on SiGe/Si staggered hetero-junctions for low-power enactment. The widely accessible commercial platform SILVACO ATLAS TCAD simulation tool was utilized to examine the enactment of a SiGe/Si staggered hetero-junction vertical TFET, including and not including a source pocket. The suggested SiGe/Si V-TFET's hetero-junction fabrication feasibility is suggested in light of recent progress in the fabrication of SiGe on pure silicon substrates [18-20].

This work proposes a Hetero-VTFET [3, 21-23] device structure and presents a comprehensive analysis of how changes in the design parameters of a device affect the performance of the proposed structure. This article focuses on the critical device design parameters that are closely linked with Hetero-VTFET. The results obtained from rigorous simulations in TCAD have been the metrics of the proposed Hetero-VTFET design. The suggested structure is studied using device parameters and work function engineering to modulate the performance and drain current characteristics simultaneously. The study is assigned into three sections: the first portion provides an introduction, the second section contains device parameters and computations from simulation results, the third section discusses the findings, and the last section includes the conclusions.

## 2. Device Parameters and Simulation Results

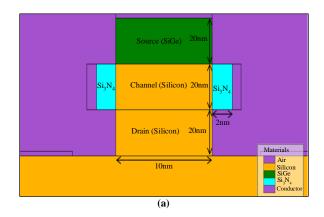

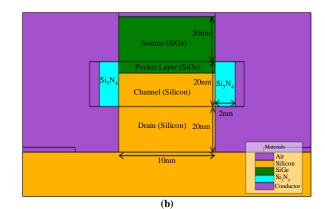

Figures 1(a) and 1(b) show a cross-sectional view of the Hetero-VTFET device with and without a pocket. Silicon is used for the channel region, and Silicon Nitride  $(Si_3N_4)$  is used as a dielectric layer due to its high dielectric constant value. The TCAD simulation of the proposed vertical TFETs in the investigation included models like the Lombardi mobility model, Bandgap narrowing, Field-dependent mobility, Shockley-Read-Hall generation-recombination, Auger recombination model, and Fermi-Dirac statistics. To enhance drain current and fabrication compliance of the proposed vertical TFETs, a high-k Si<sub>3</sub>N<sub>4</sub> material with a relative permittivity of 9.3 is employed as the gate oxide [3]. Table 1 lists the many parameters that were used in the simulation.

Fig. 1 (a) Cross-sectional view of a vertically grown SiGe Vertical Tunnel Field Effect Transistor without source packet (Hetero-VTFET WSP), (b) Schematic view of hetero-VTFET with source pocket (Hetero-VTFET SP), and (c) Calibrated output characteristic of the simulated Vertical TFET in comparison with the conventional vertical TFET [14].

| Table 1. Device design values considered for the designed hetero- |

|-------------------------------------------------------------------|

| VTFET with and without source pocket                              |

| VIFE1 with and without source pocket           |                       |                       |  |

|------------------------------------------------|-----------------------|-----------------------|--|

| Design Parameter                               | Hetero-VTFET          | Hetero-VTFET          |  |

|                                                | with Pocket           | without Pocket        |  |

| Source Doping                                  | 2e19 cm <sup>-3</sup> | 2e19 cm <sup>-3</sup> |  |

| Concentration N <sub>s</sub> [p type]          |                       |                       |  |

| Channel Doping                                 | 5e16 cm <sup>-3</sup> | 5e16 cm <sup>-3</sup> |  |

| Concentration N <sub>ch</sub> [p type]         |                       |                       |  |

| Drain Doping                                   | 5e18 cm <sup>-3</sup> | 5e18 cm <sup>-3</sup> |  |

| Concentration N <sub>d</sub> [n type]          |                       |                       |  |

| Source, Channel and                            | 20 nm                 | 20 nm                 |  |

| Drain Length                                   |                       |                       |  |

| Pocket Length (SiGe)                           | 5 nm                  | -                     |  |

| Gate Dielectric                                | 7.5                   | 7.5                   |  |

| Permittivity of Si <sub>3</sub> N <sub>4</sub> |                       |                       |  |

| Thickness of Channel                           | 10 nm                 | 10 nm                 |  |

| Metal Gate Work                                | 4.3 (eV)              | 4.3 (eV)              |  |

| Function                                       |                       |                       |  |

| Gate Dielectric Width                          | 2 nm                  | 2 nm                  |  |

| (t <sub>OX</sub> )                             |                       |                       |  |

## 3. Results and Discussion

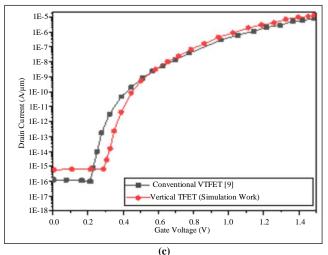

Various aspects of the Hetero-VTFET structure have been studied, including the energy band diagram, gate workfunction variation, metal gate length variation, oxide length variation, electric field, and potential and described in depth in this part. For our suggested V-TFET architectures, we first calibrated the models utilised for simulation utilizing the Silvaco TCAD tool.

The measured data presented in [18] was compared to the TCAD simulation result of Hetero-Vertical TFET. We see a reasonable alliance between the two outcomes, indicating that the chosen models are acceptable. The non-ideal observed features of the conventional Hetero-VTFET device with an oxide width of 2 nm can be ascribed to a modest mismatch between the simulation and experimental outcomes in Figure 1(c).

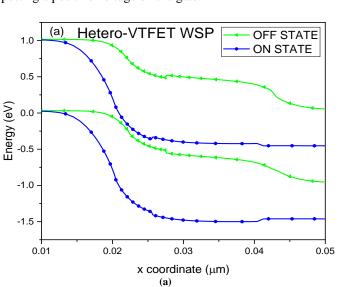

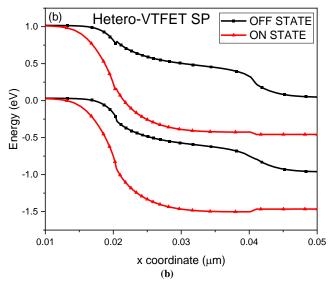

#### 3.1. Energy Band Diagram

The energy band diagram of Hetero-VTFET with and without source pockets in off-state and on-state is displayed in Figure 2. For off-state conditions, the gate voltage and drain voltage are set at  $V_{GS}=0V$  and  $V_{DS}=1V$ , whereas in on-state-these-voltages are taken as  $V_{GS}=V_{DS}=1V$ . Tunnelling does not work at zero gate bias (off-state), which means that electrons cannot move from the source to the channel through it.

There is a big band bend when the gate bias is positive in the ON state. This means that when the source has electrons in its valence band, it lines up with empty states in its conduction band. When electrons move from the source's valence band to the channel's conduction band, they tunnel through. As shown in Figure 2. When the source and the channel are connected, the SiGe/Si makes a staggered heterojunction at this point. Figures 2(a) and 2(b) show that the tunnelling via source/channel hetero-junction is boosted by putting a positive voltage on the gate.

Fig. 2 (a) Energy band diagram of Hetero-VTFET WSP in the OFF-state and ON-state, and (b) Energy band diagram of Hetero-VTFET SP in the OFF-state and ON-state.

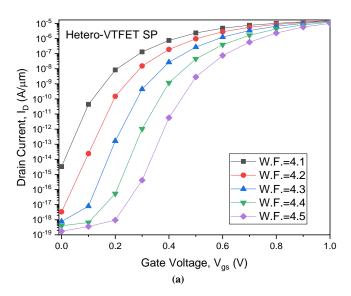

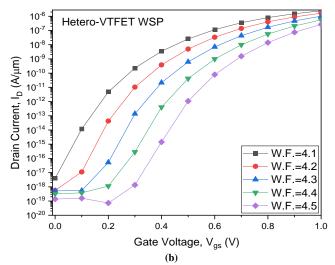

#### 3.2. Gate Work Function Variation

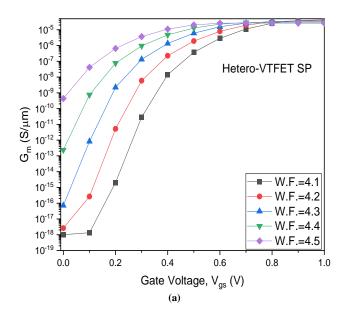

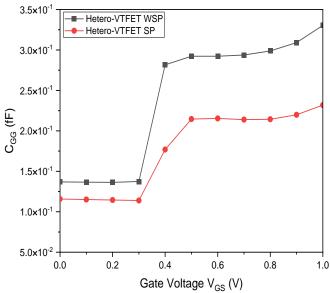

The metal gate work factor is a major factor in the determination of the device's characteristics. To see how the work function affects the device's performance, change the gate work function at a time while keeping the other parameters at the same value. There is also a separate analysis of the effect of the work functions of both structures on the drain current analysed in the figure suggested below. Outcomes comparing the transfer and output outcomes of the new Hetero-VTFETs with and without pockets to see which one is better are shown in Figures 3(a) and (b), respectively. The ION/IOFF ratios of  $2.39 \times 10^{14}$  and  $8.65 \times 10^{12}$  are attained for SiGe/Si heterojunction-based VTFET SP and VTFET WSP, respectively. Figure 3 depicts the output characteristics for which the drain voltage (Vds) is kept at 1V and the Gate Voltage (VGS) is varied from 0 to 1 V.

Fig. 3  $I_{DS}$  -V<sub>GS</sub> characteristics of (a) Hetero-VTFET SP, and (b) Hetero-VTFET WSP with variation in gate work function.

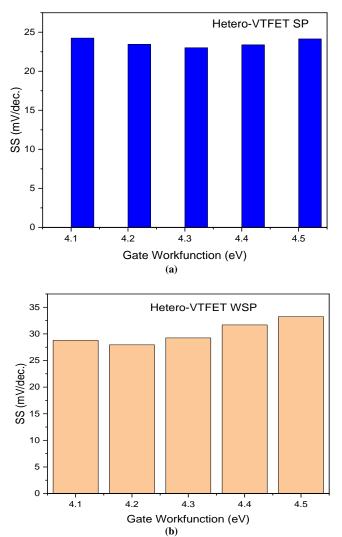

Fig. 4 Variation of Subthreshold slope (SS) of (a) Hetero-VTFET SP, and (b) Hetero-VTFET WSP with respect to gate work-function at  $V_{gs}$ =1V and  $V_{ds}$ =1 V.

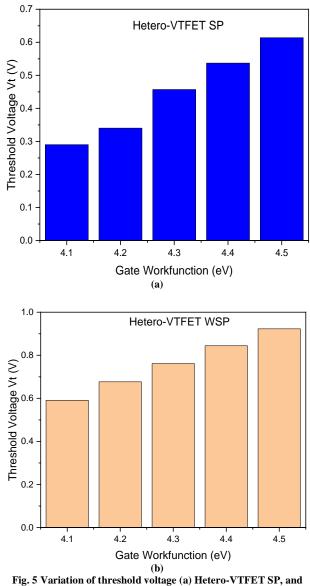

Hetero-VTFETs with and without pockets are shown in Figure 5. They are analysed using different parameters, such as IoN, IoFF, as well as threshold voltage ( $V_T$ ) and SS. In the case of Hetero-VTFET SP and WSP, the SSs are 24 mV/decade and 34 mV/decade, respectively. The gate work function is 4.5 eV for WSP and SP, both. We can see that the Hetero-VTFET SP is better than the Hetero-VTFET WSP in terms of both the IoN/IoFF ratio and the SS. When the Hetero-VTFET SP is turned on, it is worth noting that its ON current is higher than that of the Hetero-VTFET WSP.

Fig. 5 Variation of threshold voltage (a) Hetero-VTFET SP, and (b) Hetero-VTFET WSP as a gate work function.

There is, however, a big difference between the SS in the Hetero-VTFET SP and the Hetero-VTFET WSP. *I*OFF is also found to be almost the same for both Hetero-VTEFTs. This means that the Hetero-VTFET SP structure has a higher *I*ON/*I*OFF ratio than the Hetero-VTFET WSP structure, even though both Hetero-VTEFTs have almost the same OFF-state current for almost all the time. The Hetero-VTFET SP device has better subthreshold performance than the Hetero-VTFET WSP device. This proves the SP device to be more promising than the WSP device for low-power applications. When you use Hetero-VTFET SP, you can get the same amount of  $I_d$  at a lower gate voltage than with Hetero-VTFET WSP. This makes Hetero-VTFET SP a preferred option for low-voltage and low-power applications.

## 3.3. Analog/RF Analysis

In this segment, we lay a comparison of various analog Figures of Merits (FoMs) such as Transconductance (gm), gate-to-drain Capacitance (C<sub>GD</sub>), Gate-to-Source Capacitance (C<sub>GS</sub>) of both Hetero-VTFET SP and Hetero-VTFET WSP. In Figure 6(a), you can see transconductance (gm) characteristics of vertical TFETs, including and not including a pocket, of two Hetero-VTFET architectures. It is observed from Figure 6(a) that gm of Hetero-VTFET SP is reasonably greater than that of Hetero-VTFET WSP with the maximum transconductance of 72  $\mu$ S in Hetero-VTFET SP and 54  $\mu$ S in Hetero-VTFET WSP.

Hetero-VTFET SP has a larger  $g_m$  value than Hetero-VTFET WSP, which indicates that the device's capacity to convert gate voltage to drain current is superior in this arrangement. The vertical TFET-WP has a substantially larger gd than the V-TFET-WSP, including and not including pockets, respectively, in terms of output conductance. There is a greater ability to convert voltage at the drain to current at the drain in the V-TFET-WSP structure as a result of this.

## 3.3.1. Transconductance Variation

The variation of the transconductance with the variation of the gate work function of Hetero-VTFET WSP and Hetero-VTFET WP is shown in Figure 6.

Fig. 6 Transconductance characteristics of Hetero-VTFET WSP and Hetero-VTFET SP with variation in gate work function

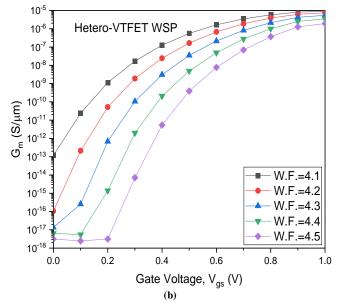

#### 3.3.2. Capacitance Variations

Figure 7 displays the comparative plot of gate capacitance along the Gate-to-Source Voltage (V<sub>GS</sub>) of VTFET WSP and VTFET WP. Total gate capacitance is a sum of Gate-to-Drain Capacitance (C<sub>GD</sub>) and Gate-to-Source Capacitance (C<sub>GS</sub>). Also, Intrinsic Gate Capacitance (C<sub>GG</sub>) is an important parameter for the radio frequency figure of merits of any TFET transistor. Contrary to traditional Metal Oxide Semiconductor Field Effect Transistors, in TFETs, C<sub>GD</sub> is denoted as parasitic or Miller capacitance, which is much larger than C<sub>GS</sub> [24], as shown in Figure 7 for both the suggested TFET devices.

Fig. 7 Comparative plot of gate capacitance ( $C_{GG}$ ) along gate-to-source voltage ( $V_{GS}$ ) of Hetero-VTFET WSP and Hetero-VTFET WP

Fig. 8 Surface potential curves of Hetero-VTFET SP and Hetero-VTFET WSP with variation in values of gate work function

Figure 7 shows the comparison of the Cgg for two proposed devices. The Cgd of the Hetero-VTFET WSP is found to be larger than that of the Hetero-VTFET SP, as reported by Uchida et al. [22]. Hetero-VTFET SP with a smaller  $C_{GG}$  has superior circuit-level performance because of smaller parasitic effects, which were explored subsequently. Hetero-VTFET WSP has a higher  $C_{GG}$  value than Hetero-VTFET SP, even though the  $C_{GS}$  values in Figure 7 appear to be virtually identical for the two devices.

## 3.4. Surface Potential

The variation of the surface potential with the gate work function is plotted in Figure 8. It is observed that larger values of the gate work function result in lower surface potential at the source-channel interface. This is because the energy level difference between the source's valance band and the channel's conduction band reduces as the gate work function grows. The decreasing energy level difference results in a greater tunnelling barrier, which reduces the surface potential. The surface potential varies with the gate capacitance of the device.

Figure 8 shows the comparison of the surface potential for two proposed devices. The potential of the Hetero-VTFET WSP is found to be larger than that of the Hetero-VTFET SP. Figure 8 shows the comparative plot of surface potential with respect to a gate work function in which we found that as we increase the gate work function of both hetero-junctions structures the surface potential starts falling.

#### 4. Conclusion

The article discusses the DC and RF characteristics of V-TFETs based on SiGe/Si hetero-junctions, including and not including source pockets. The simulation results demonstrate that the VTFET with Source Pocket (SP) structure has a lower SS ((~23 mV/decade), a lower threshold voltage (0.28 V), and a higher ION/IOFF ratio (~  $10^{14}$ ) than the V-TFET without pocket being included (WSP) structure's corresponding values (~32 mV/decade, 0.59 V, and ~  $10^{12}$ ). Due to the proposed device's extremely low OFF-state current, both devices exhibit a higher ION/IOFF ratio on the order of (~ $10^{12}$ ) than previous heterojunction-based TFETs.

The Hetero-VTFET-SP structure suggested here offers superior thermal stability to the structure with no pocket included. The analog/RF research demonstrates that the SP structure of Hetero-VTFET outperforms the WSP structure of Hetero-VTFET. Additionally, we demonstrate that our proposed SiGe/Si heterojunction-based Hetero-VTFET SP device has superior analogue performance parameters compared to certain previously reported results for alternative TFET designs.

## References

- R.H. Yan, A. Ourmazd, and K.F. Lee, "Scaling the Si MOSFET: From Bulk to SOI to Bulk," *IEEE Transactions on Electron Devices*, vol. 39, no. 7, pp. 1704-1710, 1992. [CrossRef] [Google Scholar] [Publisher Link]

- [2] Alan C. Seabaugh, and Qin Zhang, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2095-2110, 2010. [CrossRef] [Google Scholar] [Publisher Link]

- [3] Tejas Krishnamohan et al., "Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) with Record High Drive Currents and <60 mV/dec Subthreshold Slope," 2008 IEEE International Electron Devices Meeting, San Francisco, USA, 2008, pp. 947-949, 2008. [CrossRef] [Google Scholar] [Publisher Link]

- [4] P.F. Wang et al., "Complementary Tunneling Transistor for Low Power Application," *Solid-State Electronics*, vol. 48, no. 12, pp. 2281-2286, 2004. [CrossRef] [Google Scholar] [Publisher Link]

- [5] Kathy Boucart, and Adrian Mihai Ionescu, "Double Gate Tunnel FET with High k Gate Dielectric," *IEEE Transactions on Electron Devices*, vol. 54, no. 7, pp. 1725-1733, 2007. [CrossRef] [Google Scholar] [Publisher Link]

- [6] M. Jagadesh Kumar, and Sindhu Janardhanan, "Doping-Less Tunnel Field Effect Transistor: Design and Investigation," IEEE Transactions on Electron Devices, vol. 60, no. 10, pp. 3285-3290, 2013. [CrossRef] [Google Scholar] [Publisher Link]

- [7] Uygar E. Avci, Daniel H. Morris, and Ian A. Young, Tunnel Field-Effect Transistors: Prospects and Challenges," *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 88-95, 2015. [CrossRef] [Google Scholar] [Publisher Link]

- [8] K.K. Bhuwalka, J. Schulze, and I. Eisele, "A Simulation Approach to Optimize the Electrical Parameters of a Vertical Tunnel FET," *IEEE Transactions on Electron Devices*, vol. 52, no. 7, pp. 1541-1547, 2005. [CrossRef] [Google Scholar] [Publisher Link]

- [9] Sneh Saurabh, and M. Jagadesh Kumar, "Impact of Strain on Drain Current and Threshold Voltage of Nanoscale Double Gate Tunnel Field Effect Transistor," *Japanese Journal of Applied Physics*, vol. 48, no. 6, 2009. [CrossRef] [Google Scholar] [Publisher Link]

- [10] Anne S. Verhulst et al., "Complementary Silicon-Based Hetero-Structure Tunnel-FETs with High Tunnel Rates," *IEEE Electron Device Letters*, vol. 29, no. 12, pp. 1398-1401, 2008. [CrossRef] [Google Scholar] [Publisher Link]

- [11] T. Krishnamohan et al., "High-Mobility Low Band-to-Band Tunneling Strainedgermanium Double-Gate Heterostructure FETs: Simulations," *IEEE Transactions on Electron Devices*, vol. 53, no. 5, pp. 1000-1009, 2006. [CrossRef] [Google Scholar] [Publisher Link]

- [12] Sneh Saurabh, and M. Jagadesh Kumar, "Estimation and Compensation of Process Induced Variations in Nanoscale Tunnel Field Effect Transistors (TFETs) for Improved Reliability," *IEEE Transactions on Device and Materials Reliability*, vol. 10, no. 3, pp. 390-395, 2010. [CrossRef] [Google Scholar] [Publisher Link]

- [13] Dawit B. Abdi, and M. Jagadesh Kumar, "Controlling Ambipolar Current in Tunneling FETs Using Overlapping Gate-On-Drain," *IEEE Journal of the Electron Devices Society*, vol. 2, no. 6, pp. 187-190, 2014. [CrossRef] [Google Scholar] [Publisher Link]

- [14] Jung-Shik Jang, and Woo Young Choi, "Ambipolarity Factor of Tunneling Field Effect Transistors (TFETs)," Journal of Semiconductor Technology and Science, vol. 11, no. 4, pp. 272-277, 2011. [CrossRef] [Google Scholar] [Publisher Link]

- [15] Kaushal Nigam, Pravin Kondekar, and Dheeraj Sharma, "High Frequency Performance of Dual Metal Gate Vertical Tunnel Field Effect Transistor Based on Work Function Engineering," *Micro & Nano Letters*, vol. 11, no. 6, pp. 319-322, 2016. [CrossRef] [Google Scholar] [Publisher Link]

- [16] Hao Wang et al., "A Novel Barrier Controlled Tunnel FET," IEEE Electron Device Letters, vol. 35, no. 7, pp.798-800, 2014. [CrossRef] [Google Scholar] [Publisher Link]

- [17] Lingquan Wang et al., "Design of Tunneling Fieldeffect Transistors Based on Staggered Heterojunctions for Ultralow-Power Applications," *IEEE Electron Device Letters*, vol. 31, no. 5, pp. 431-433, 2010. [CrossRef] [Google Scholar] [Publisher Link]

- [18] Atlas User's Manual Device Simulation Software, Silvaco International, Santa Clara, USA, 2016. [Online]. Available: https://www.eng.buffalo.edu/~wie/silvaco/atlas\_user\_manual.pdf

- [19] Evgeniy Chusovitin et al., "Formation of a Thin Continuous GaSb Film on Si (001) by Solid Phase Epitaxy," *Nanomaterials*, vol. 8, no. 12, pp. 1-11, 2018. [CrossRef] [Google Scholar] [Publisher Link]

- [20] D.L. Goroshko et al., "Solid Phase Epitaxy Formation of Silicon-GaSb Based Heterostructures," JJAP Conference Proceedings, vol. 5, 2017. [CrossRef] [Google Scholar] [Publisher Link]

- [21] S. Song et al., "Laser Restructuring and Photoluminescence of Glassclad GaSb/Si-Core Optical Fibres," *Nature Communications*, vol. 10, pp. 1-7, 2019. [CrossRef] [Google Scholar] [Publisher Link]

- [22] H. Uchida et al., "Reduction of Dislocation Density by Thermal Annealing for GaAs/GaSb/Si Heterostructure," *Journal of Crystal Growth*, vol. 150, pp. 681-684, 1995. [CrossRef] [Google Scholar] [Publisher Link]

- [23] C. Convertino et al., "III-V Heterostructure Tunnel Field-Effect Transistor," Journal of Physics: Condensed Matter, vol. 30, 2018. [CrossRef] [Google Scholar] [Publisher Link]

- [24] Yue Yang et al., "Tunneling Field-Effect Transistor: Capacitance Components and Modeling," *IEEE Electron Device Letters*, vol. 31, no.

7, pp. 752-754, 2010. [CrossRef] [Google Scholar] [Publisher Link]